# Numerical Linear Algebra Algorithms on Vector and Parallel Computers

LARS ELDEN AND HAESUN PARK

서울대학교 수학연구소·대역해석학 연구센터 Notes of the Series of Lecture held at the Seoul National University

Lars Elden, Linköping University, S-581 83 Linköping, Sweden Haesun Park, University of Minnesota, Minneapolis, MN 55455, U.S.A.

퍼낸날: 1993년 8월 14일

지은이: Lars Eldén and Haesun Park

퍼낸곳: 서울대학교 수학연구소·대역해석학연구센터[TEL:02-880-6530]

# Contents

| 1 | Introduction              |                                        |    |  |  |  |  |  |  |

|---|---------------------------|----------------------------------------|----|--|--|--|--|--|--|

|   | 1.1                       | What is a Supercomputer?               | 5  |  |  |  |  |  |  |

|   | 1.2                       | Why Supercomputers?                    | 6  |  |  |  |  |  |  |

| 2 | Architecture              |                                        |    |  |  |  |  |  |  |

|   | 2.1                       | Basic concepts                         | 9  |  |  |  |  |  |  |

|   | 2.2                       |                                        |    |  |  |  |  |  |  |

|   |                           | 2.2.1 Pipelining                       | 14 |  |  |  |  |  |  |

|   |                           | 2.2.2 Vector Register and Instructions | 15 |  |  |  |  |  |  |

|   |                           | 2.2.3 Chaining                         | 18 |  |  |  |  |  |  |

|   |                           | 2.2.4 Indirect Addressing              | 21 |  |  |  |  |  |  |

|   |                           | 2.2.5 Conditional Statements           | 22 |  |  |  |  |  |  |

|   | 2.3                       | Memory Organization                    | 23 |  |  |  |  |  |  |

|   |                           | 2.3.1 Interleaved Memory               | 23 |  |  |  |  |  |  |

|   |                           | 2.3.2 Memory Hierarchy                 | 25 |  |  |  |  |  |  |

|   | 2.4                       | Shared Memory Parallel Computers       | 26 |  |  |  |  |  |  |

|   | 2.5                       | Distributed Memory Parallel Computers  |    |  |  |  |  |  |  |

|   |                           | 2.5.1 Interconnection Networks         | 28 |  |  |  |  |  |  |

|   | 2.6                       | SIMD and MIMD Parallel Computers       | 30 |  |  |  |  |  |  |

|   | 2.7                       | Performance Measurements               | 31 |  |  |  |  |  |  |

|   |                           | 2.7.1 Speedup and Efficiency           | 31 |  |  |  |  |  |  |

|   |                           | 2.7.2 Amdahl's Law                     | 32 |  |  |  |  |  |  |

|   |                           | 2.7.3 Scaled Speed-up                  | 35 |  |  |  |  |  |  |

|   | 2.8                       | Important Issues in Parallel Computers | 36 |  |  |  |  |  |  |

| 3 | Vectorization and Fortran |                                        |    |  |  |  |  |  |  |

| - | 3.1                       | Introduction                           | 37 |  |  |  |  |  |  |

| 4 |  | CONTENTS |

|---|--|----------|

|   |  |          |

| 3.2 Storage of Matrices                         | 37 |  |  |  |  |  |  |  |

|-------------------------------------------------|----|--|--|--|--|--|--|--|

| 3.3 Fortran 90                                  | 39 |  |  |  |  |  |  |  |

| 3.3.1 Vectors and Matrices                      | 39 |  |  |  |  |  |  |  |

| 3.3.2 Array Sections                            | 39 |  |  |  |  |  |  |  |

| 3.3.3 Vector Mask Operations                    | 42 |  |  |  |  |  |  |  |

| 3.4 Vectorization of Loops                      | 42 |  |  |  |  |  |  |  |

| 3.4.1 Vector Reference                          | 43 |  |  |  |  |  |  |  |

| 3.4.2 Indirect Addressing                       | 44 |  |  |  |  |  |  |  |

| 3.4.3 Scalar Temporary Variables                | 44 |  |  |  |  |  |  |  |

| 3.4.4 Recursion                                 | 45 |  |  |  |  |  |  |  |

| 3.4.5 Reduction of a Vector to a Scalar         | 47 |  |  |  |  |  |  |  |

| 3.4.6 Rounding Errors                           | 49 |  |  |  |  |  |  |  |

| 3.4.7 Vectorization Inhibitors                  | 49 |  |  |  |  |  |  |  |

| 4 Algorithms on Vector Computers                | 51 |  |  |  |  |  |  |  |

| 4.1 Matrix Multiplications                      | 51 |  |  |  |  |  |  |  |

| 4.1.1 Matrix-vector Product                     | 51 |  |  |  |  |  |  |  |

| 4.1.2 Matrix Multiplication                     | 55 |  |  |  |  |  |  |  |

| 4.2 BLAS: Basic Linear Algebra Subprograms      | 56 |  |  |  |  |  |  |  |

| 4.3 Linear Systems of Equations                 | 60 |  |  |  |  |  |  |  |

| 4.3.1 Gaussian Elimination and LU Decomposition | 60 |  |  |  |  |  |  |  |

| 4.3.2 Block Algorithms for LU Decomposition     | 63 |  |  |  |  |  |  |  |

| 4.3.3 LAPACK                                    | 67 |  |  |  |  |  |  |  |

| 5 Algorithms on Distributed-memory Computers    | 71 |  |  |  |  |  |  |  |

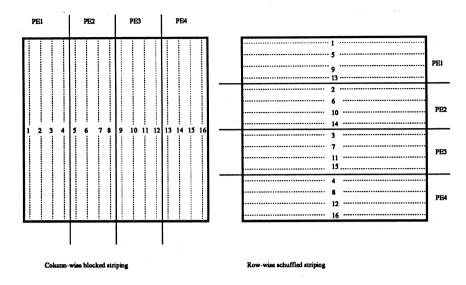

| 5.1 Load-Balancing                              | 71 |  |  |  |  |  |  |  |

| 5.1.1 Mapping Matrices to Processors            | 71 |  |  |  |  |  |  |  |

| 5.2 Message-Passing Systems                     | 73 |  |  |  |  |  |  |  |

| 5.2.1 Matrix Multiplications                    | 74 |  |  |  |  |  |  |  |

| 5.2.2 Gaussian Elimination                      | 76 |  |  |  |  |  |  |  |

| 5.2.3 Triangular Systems                        | 80 |  |  |  |  |  |  |  |

| 5.3 Data-Parallel Computations                  | 82 |  |  |  |  |  |  |  |

| 5.3.1 Distributed-Shared Memory                 | 82 |  |  |  |  |  |  |  |

| 5.3.2 Gaussian Elimination                      | 83 |  |  |  |  |  |  |  |

| 5.3.3 Matrix Multiplication                     | 86 |  |  |  |  |  |  |  |

| 5.4 Jacobi Method for Eigendecomposition        | 89 |  |  |  |  |  |  |  |

| Bibliography                                    |    |  |  |  |  |  |  |  |

# Chapter 1

# Introduction

# 1.1 What is a Supercomputer?

There is no formal definition of a supercomputer, but a common way of explaining the concept is to say that a supercomputer is a computer of which the peak performance is at least 10% of the presently fastest existing computer. This makes the definition a loose one, which changes over time, and this is reasonable since the development of supercomputers is very fast: The performance of a powerful, expensive and big supercomputer some ten years ago can now be found in a relatively cheap desktop computer that is available for use by a single researcher or engineer.

A similar, loose definition is the following: a supercomputer is a very powerful computer, at least two orders of magnitudes more powerful in terms of speed and storage than a conventional computer.

To illustrate the aspect of speed, we cite the following performance figures from a commonly used computer benchmark, namely the LINPACK benchmark [5]. In that test the performance of computers is measured from the execution times when two linear systems of equations are solved: the first is of dimension 100 and is solved using a subroutine from the LINPACK library[3]. The second is larger (dimension 1000) and here any program (i.e., even heavily optimized) can be used. Below we give timings in Mflops (million floating point operations per second) for some supercomputers and workstations.

This shows that for the fastest supercomputers and workstations (April 1992) and for problems that are worth solving on supercomputers (i.e., problems that are large in some sense, usually in terms of the number of floating

| Computer                    | n = 100 | n = 1000 | Peak performance |

|-----------------------------|---------|----------|------------------|

| Cray Y-MP C90 (16 proc.)    | 479     | 9715     | 15238            |

| NEC SX-3/44R (4 proc.)      |         | 15120    | 25600            |

| Fujitsu VP2600/10 (1 proc.) | 249     | 4009     | 5000             |

| IBM Risc/6000-560           | 31      | 84       | 100              |

| SUN SPARCstation IPX        | 4.1     |          |                  |

Table 1.1: LINPACK Benchmark for various computers, May 31, 1993.

points operations that are needed) it is really true that the supercomputers are two orders of magnitude faster.

Since there is no real definition of the term "supercomputer", and since it gives the impression that a particular computer is something special, it can be used by computer manufacturers as a marketing trick. Therefore, many prefer the term "high performance computer", which can be interpreted in a wider sense, and is less prestigious. We will use the term supercomputer in the sequel.

Supercomputers are made fast by introducing parallelism on different levels in the architecture. We will refer to non-supercomputers as *conventional* or **sequential computers**, although such computers normally have some parallel features (especially on a low level of the hardware), but to a lesser extent than supercomputers. The first computer, which was labeled supercomputer, was the Cray-1. This machine appeared in 1976.

# 1.2 Why Supercomputers?

Supercomputers are designed to be very fast and are intended for problems that would otherwise be intractable. Here we will give two examples of applications, where the use of supercomputers is essential.

In the description of the examples we will use the terms Mflops and Gflops, which are used as measures of the speed of fast computers. 1 Mflops and 1 Gflops are the same as 10<sup>6</sup> and 10<sup>9</sup> floating point operations per second, respectively.

The first example is the simulation of car crashes where a car hits a wall at a speed of 60 km/h. The model of the car has approximately 20 000 elements, with 6 degrees of freedom (unknowns) for each element, i.e., 120 000 unknowns altogether. The crash is simulated during 120ms, and 150 000 time

steps are taken. In each time step around 100 floating point operations (flops) are needed per unknown. This means that the total computation requires  $1.2 \cdot 10^5 \cdot 1.5 \cdot 10^5 \cdot 10^2 \approx 2 \cdot 10^{12}$  flops. On a computer with a speed of 1 Mflops this would take  $2 \cdot 10^6$  seconds or 25 days approximately. This is too much in a product development stage, when it is necessary to evaluate several alternative constructions. On the other hand, with a supercomputer that can run at 1 Gflops, the same computation takes about 35 minutes, which is acceptable.

The second example is concerned with the flow around the Hermes space-shuttle. In this computation there are around  $10^6$  grid points and 5 unknowns per point.  $10^4$  time steps are taken and for each grid point and step  $10^3$  flops are needed. This adds up to  $5 \cdot 10^{13}$  flops altogether, and from the previous example we see that this needs a computer with a speed of at least 1 Gflops to be feasible.

In reducing computation time in a rate that is comparable to the improvement seen since 1950's, it is necessary to use parallelism. From 1950 to the mid 1970's, the improvement of an order of  $10^5$  was made in speed, which was due to improvements in the clock cycle and in architecture and design. Since gains from the improvement in semiconductor technology are becoming much harder, parallelism is the only means for making orders of magnitude improvement in computing speed. The hardware to deliver such performances have been built but they are not easy to exploit efficiently. Therefore, the users have to understand the architecture and be able to redesign their algorithms to benefit fully from new technology.

# Chapter 2

# Architecture

# 2.1 Basic concepts

We shall here briefly discuss same basic concepts that are needed in the sequel for describing supercomputers and for discussing their performance. Since the emphasis of this text is the use of supercomputers for linear algebra problems rather than the construction of supercomputers, we will not go into details concerning hardware.

Earlier we have introduced the measures of speed Mflops and Gflops. Now we will discuss the concept of cycle time, and its relation to the measures of speed.

Time in a digital computer should be considered to be *discrete*: all events take place at distinct points in time, and the **cycle time** is the constant time between these points. The fastest a sequential (i.e. non-parallel) computer can execute is one instruction per clock cycle. So, if the cycle time is 4 ns (1 ns is  $10^{-9}$  second), then the maximum speed is  $1/(4 \cdot 10^{-9}) = 2.5 \cdot 10^8$  instructions per second, i.e., 250 Mips (1 Mips is 1 million instructions per second).

Similarly, if the floating point arithmetic units of a computer can deliver one result per clock cycle, then the maximum theoretical speed for floating point operations is 1 over the cycle time. Thus, a computer with a cycle time of 4 ns can have a maximum theoretical speed of 250 Mflops (under the above assumption). Later we will see that it is possible to double that figure (or even increase it by a larger factor) by introducing more parallelism.

It is interesting to note that the cycle times of supercomputers has not been decreased very much, since the first supercomputer, the Cray-1, was introduced in 1976. The Cray-1 had a cycle time of 12.5 ns. The presently fastest supercomputers have cycle times of the order of a couple of nanoseconds. However, present day machines are at least a factor 100 faster than the Cray-1; it is obvious then that this increase in speed is explained by a higher degree of parallelism than in the Cray-1.

In principle, a signal that is sent from one part of the computer should be able to reach any other part during one clock cycle. Therefore, the speed of light is one factor that limits performance. The computer must be so small that signals can reach their destination during one cycle. To give an idea of the distances involved, we note that the distance traveled by light in 1 ns is about 30 cm.

To illustrate scalar computations we take the simplest possible example, the addition of to real numbers,

$$s1=s2+s3$$

The machine operations needed to execute this statement are (we use an informal assembler type notation here and in the sequel; the number of cycles given are only meant to be an example).

# Number of cycles

Sequential computers do everything in scalar mode. Thus the execution of the following program

```

do i=1,1000

s1(i)=s2(i)+s3(i)

enddo

```

takes 9000 cycles plus the overhead for the loop.

In the next section we will discuss how the time for this loop can be reduced by parallelism. Later we will deal extensively with vectors: a **vector** is an ordered list of scalars. When a vector is used in a loop, this is often done with a constant distance, **stride**, between the elements referenced. In the code below, the vector is referenced with stride 1 on the first loop, and stride 3 in the second.

```

do i=1,1000

a(i)=....

enddo

do i=1,1000,3

b(i)=....

enddo

```

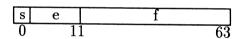

A word is the basic unit of information that is addressed in a computer. The IEEE standard for binary floating point arithmetic was adopted in 1985. It defines four floating point formats in two groups, basic and extended, each with two widths, single and double. The organization of the double precision basic format is shown in Figure 2.1.

Figure 2.1: Basic format, IEEE double precision.

The components are the sign s (one bit), the exponent e (eleven bits), and the fraction f (52 bits), altogether 64 bits. The value v of a floating point number x is

$$v = (-1)^s (1.f) 2^{e-1023}$$

for  $0 < e < 2047$ ,

We see that the leading bit of the significant, i.e., the one to the left of the binary point, is not stored, since due to the normalization it is known always to be equal to one. Thus, one extra bit is gained for the fraction. The largest and smallest positive numbers that can be represented are  $2^{1023}(2-2^{-52}) \approx 9 \cdot 10^{307}$  and  $2^{-1022} \approx 2 \cdot 10^{-308}$ , respectively. Implementations of the standard provide the addition, subtraction, multiplication, division and square root operations, as well as binary-decimal conversions. Except for the conversions, all operations give a result that is equal to the rounded result of the corresponding operation correct to infinite precision.

Most modern computers implement the IEEE standard (the Cray Research supercomputers are a notable exception: their word length is 64 bits, but they have a different floating point format), and since most supercomputers have word length 64, their normal floating point format is double precision.

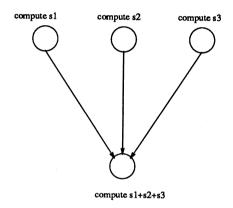

As a first example of parallel computations we consider the problem of computing an inner product of two vectors  $x \in \mathbb{R}^n$  and  $y \in \mathbb{R}^n$ ,

$$s = \sum_{1}^{n} x_i y_i \tag{2.1}$$

A typical algorithm would look like

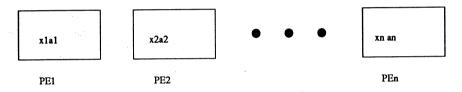

Although indices are referenced in the order of  $1, 2, \dots, n$ , there are numerous other ways of arranging them. If p processors are available for the computation and m = n/p, we can rearrange the above as

```

do j = 1, p in parallel

s(j) = 0

do i = (j-1)*m+1, j*m

s(j) = s(j) + x(i)*y(i)

enddo

enddo

s = 0

do j = 1, p

s = s + s(j)

enddo

```

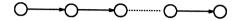

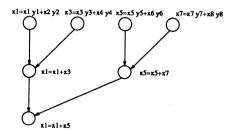

When there are more processors, we can apply the above idea recursively and design a better parallel algorithm.

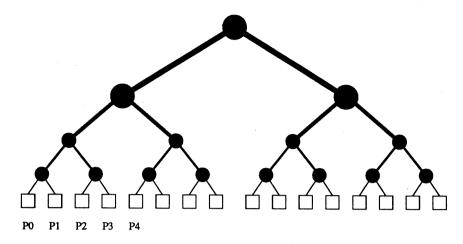

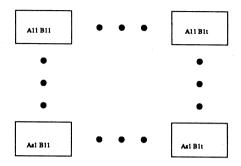

A dependency graph is a graph that represents the dependence among tasks in an algorithm. The nodes in the graphs represent the tasks in the algorithm and the directed edge from node i to node j represents that task j can start only after task i is completed. The following three figures show the dependency graph of the above inner product algorithms. The graphs allow us to identify the tasks that can be executed in parallel. The height of the graph represents the minimum number of sequential steps in the algorithm.

Figure 2.2: Dependency graph 1

Figure 2.3: Dependency graph 2

Figure 2.4: Dependency graph 3

## 2.2 Forms of Parallelism

#### 2.2.1 Pipelining

We will use the term functional unit for the hardware that performs different arithmetic and logical operations in the supercomputer. We are mainly interested in the floating point addition, multiplication and division operations. In this section, we discuss how these operations are efficiently executed on many modern computers using pipelined functional units. This concept is described with addition as an example.

To introduce the concept of a pipeline, consider an assembly line for making cars, and assume, for simplicity, that the line has only three stages, each of which takes equally long (one time unit).

The normal operation of such an assembly line is to input enough material for one car into the procedure every time unit, so that the workers are active all the time and produce one car every time unit.

Next, consider floating point addition. The following example shows that floating point addition can be divided into stages:

$$1.234 \cdot 10^{0} + 4.567 \cdot 10^{-2} = (1.234 + 0.04567) \cdot 10^{0} = 1.27967 \cdot 10^{0} = 1.280 \cdot 10^{0}.$$

For simplicity, we assume here three stages:

$$\begin{array}{c|c} x \longrightarrow & \text{adjust exponents} \\ y \longrightarrow & \text{and shift} & \longrightarrow & \text{add the} \\ \end{array}$$

Assume that each stage takes one clock period. When the sum of two vectors z := x + y (i.e.,  $z_i := x_i + y_i$ , i = 1, 2, ..., n) is computed in a computer with pipelined floating point arithmetic, then the addition unit is operated like a car assembly line, a **pipeline**: with a pair of input operands every clock period (after an initial startup time), an output is produced every clock period.

At a certain point in the computation, the operands have progressed through the pipeline as illustrated below.

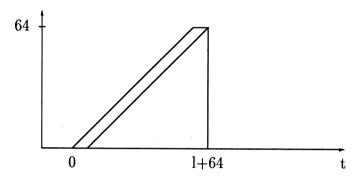

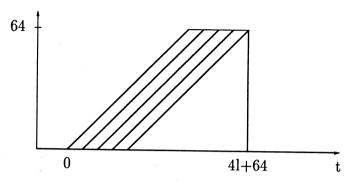

After 3 cycles the first result emerges from the pipeline, and then one result is produced every clock cycle. A timing diagram for a pipelined operation is given in Figure 2.5

Figure 2.5: Timing diagram for a pipelined operation with n = 64. The pipelength is assumed to be l.

The computation in **vector mode** of the sum of the two vectors takes l + n clock periods, where l is the length (in cycles) of the pipeline and n is the vector length. The corresponding computation in **scalar mode** (without pipelining) would take ln clock periods.

### 2.2.2 Vector Register and Instructions

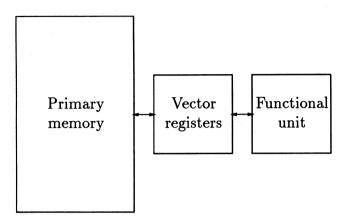

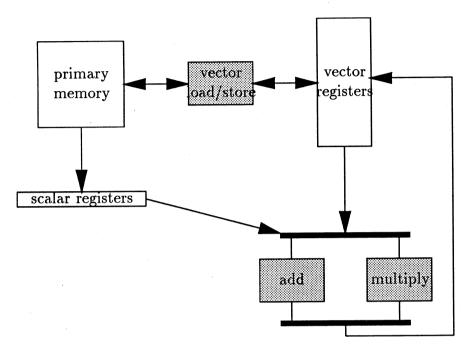

Pipelined functional units can produce one result every clock period, but they also need operands at the same rate. It is very expensive to construct memories that can deliver operands at this rate, and therefore most modern supercomputers with pipelined arithmetic have **vector registers**, which can be considered as intermediate storage between the functional units and the primary memory.

In the Cray X-MP (and Y-MP) processor, there are 8 vector registers, each with 64 elements. For our examples with vector registers we will assume that they are of size 64.

The vector registers are used in **vector instructions**. As an example, consider the following code:

Figure 2.6: Vector registers are intermediate, fast storage units between primary memory and functional units.

$$a(i)=b(i)+c(i)$$

enddo

On computers with vector instructions the (informal) assembler code for this is:

Thus, there are only four machine instructions. We also give a more detailed assembler version of the same code:

Here b(1) is the **start address** in memory of the vector b, 64 is the **vector length** (we assume that the vector registers have 64 elements), and 1 denotes the *stride*.

Typically, a vector instruction reserves the output vector register for as long as the operation takes, and the input vector registers until the last element has been delivered to the vector functional unit.

We say that a computation **vectorizes** if it can be performed with vector instructions (operations). A compiler that can take a program written in a high level language and produce code with vector instructions is called a **vectorizing compiler**.

Note that a vector operation can not be stopped once it has started: as many operations will be performed as the vector length indicates. Therefore, loops with conditional statements cannot be vectorized (we will see later that there are methods that circumvent this problem).

A more serious difficulty is recursion:

```

do i=1,n

x(i)=y(i)+x(i-1)

enddo

```

The same vector register can not be used both for input and output to the floating point functional unit, and therefore recursion can not be vectorized.

If the number of operations in a vector operation is larger than the length of the vector registers, then the loop must be divided up in sub-loops. Consider, e.g.,

```

do i=1,n

x(i)=y(i)*z(i)

enddo

```

where n > 64. The compiler must generate machine code, where the vector instructions have vector length equal to the length of the vector registers, i.e., 64 in our examples. Thus, the above code is replaced by the following:

This technique is called strip-mining.

Let l denote the startup and unit time for a certain vector operation, i.e. the time to set up the vector instruction plus the time for the first pair of operands to pass through the pipeline. Then, the time to perform that operation on vectors with length n is

$$t = (l+n)t_{\rm c},$$

where  $t_c$  is the clock period. The rate of producing n results is

$$r_n = \frac{n}{(l+n)t_c}.$$

The maximum (or asymptotic) rate is obtained by letting n tend to infinity:

$$r_{\infty} = \frac{1}{t_{\mathbf{c}}}.$$

Another interesting parameter is the half performance length  $n_{1/2}$  which is the vector length required to achieve half the maximum performance. This can be determined from the equation

$$\frac{n}{(l+n)t_{\rm c}} = \frac{r_{\infty}}{2} = \frac{1}{2t_{\rm c}},$$

which gives

$$n_{1/2}=l.$$

It is very important to have a short start up and unit time l, since this determines the performance for relatively short vectors.

#### 2.2.3 Chaining

Other vector operations that can be pipelined are (componentwise) multiplication  $z_i := x_i * y_i$ , i = 1, 2, ..., n, and division  $z_i := y_i/x_i$ , i = 1, 2, ..., n. It

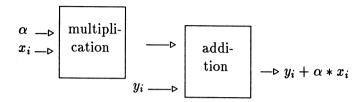

is also common that two arithmetic functional units can be chained together to form a single pipeline. By chaining the multiplication and addition units,

the computation of the so-called Saxpy operation,

where s is a scalar, can be performed in vector mode, i.e., so that one result is produced every clock period. Similarly, the code

can be chained.

On the vector instruction level we have (assuming that appropriate vector loads have been performed)

Chaining means that immediately after the vector multiplication has started, the addition is issued. However, it can not start until the first result has appeared from the multiplication pipeline. At the same time as the first result reaches V3 it also goes into the addition pipeline, and the addition can start. During this chained operation the multiplication and addition functional units work in *parallel* in a carefully synchronized manner.

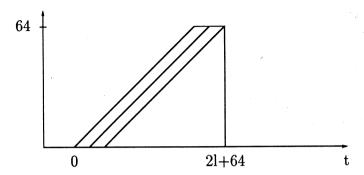

In Figure 2.7 we give a timing diagram for two chained vector operations. For simplicity we assume that both operations have equal start up and unit times.

Figure 2.7: Timing diagram for two chained vector operations.

It is seen that after 2l cycles the result of two floating point operations is output every cycle. Therefore, on a computer where floating point addition and multiplication can be chained, the peak performance is

$$r_{\infty}=rac{2}{t_{c}},$$

where  $t_c$  is the cycle time.

#### Example:

The CRAY X-MP has clock period  $t_c = 8.5$  ns. This gives an asymptotic rate for, e.g., vector (componentwise) multiplication of  $r_{\infty} = 1/8.5 \cdot 10^{-9} \approx 117$  Mflops (1 Mflop =  $10^6$  floating point operations).

The startup time l for multiplication is l = 9 clock periods. Therefore, the half performance length is  $n_{1/2} = 9$ . This indicates that the CRAY X-MP is very fast for short vectors also.

For the chained SAXPY operation  $y := y + \alpha * x$ , the asymptotic rate is  $r_{\infty} \approx 234$  Mflops, since here the result of two arithmetic operations is output every clock period.

It should be emphasized that the values of these parameters are only theoretical. In practice, one has to take into account the time for memory accesses. The measured values are  $r_{\infty} = 70$ ,  $n_{1/2} = 53$  for vector multiplication, and  $r_{\infty} = 148$ ,  $n_{1/2} = 60$  for the SAXPY operation (from [11]).

#### 2.2.4 Indirect Addressing

In sparse matrices, the majority of the elements are equal to zero. It is common in applications that such matrices are of the order  $10^5 - 10^6$ , but the number of nonzero elements is less than 5%. For sparse matrices the usual matrix storage scheme should not be used, since the whole primary memory and much secondary memory would be wasted for storing zeros. Instead only the nonzero elements are stored, together with information about their location in the matrix.

In such applications the following type of code appears quite often:

```

do i=1,64

a(jj(i))=b(jj(i))+s*c(jj(i))

enddo

```

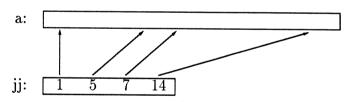

jj is a vector of indices to elements in the vectors a, b, and c:

Figure 2.8: The vector jj with addresses elements in a.

This is called **indirect addressing**. Many computers have vector instructions for indirect addressing operations:

#### 2.2.5 Conditional Statements

As we said earlier, vector instructions cannot be interrupted. This means that in order to vectorize conditional statements, special arrangements are needed. The vector mask (VM) register is a register with 64 positions, each one bit wide. It can be used to vectorize the following type of statements.

```

do i=1,n

if (a(i) > 0) x(i)=y(i)*a(i)

enddo

```

The following assembler code illustrates how the VM register is used.

All instructions are vector operations. On some computers (but not on Cray's) arbitrary vector operations can be controlled by the VM register.

There are two problems with this construct:

- If only a few of the conditions are true, then many arithmetic operations are wasted. It may be much faster to execute the loop using scalar instructions. Note that the compiler cannot decide this in advance.

- It can not be used for codes of the type

do i=1,n

if

$$(a(i) > 0) x(i)=y(i)/a(i)$$

enddo

since that would lead to division by zero.

# 2.3 Memory Organization

We start this section with a quotation from one of the pioneers in the early history of the digital computer.

In my opinion this problem of making a large memory available at reasonably short notice is much more important than that of doing operations such as multiplication at high speed. (Alan Turing, 1947)

This statement is equally true today: to balance the speed of the floating point functional units and the parallel features (multiple pipelines, multiple processors), very large memories are needed, typically of the order 0.1 to 1 Gwords (1 Gwords is 10<sup>9</sup> words (64 bit)). Since the fast memory is very expensive, compromises have to be made between size and speed.

Typically, the memory cycle time (the time it takes for one word to be transferred from memory to a register) is larger than one cycle. For example, on the Cray X-MP it is four cycles. It is obvious that with such a memory speed, the vector load (and store) operations cannot deliver operands to (and from) vector registers with a speed that matches that of the vector floating operations (this is needed if memory accesses and floating point operations are to be chained, as shown earlier).

In order to increase the performance of the memory, it is divided into separate units, which can operate in parallel. Such memory organization is called **interleaved**, see the next section.

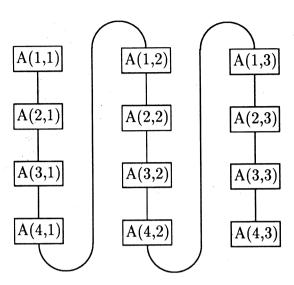

As memory access patterns are important on high performance computers, we need to specify here how matrices are stored in primary memory. In Fortran, which is the most commonly used language for scientific computations, matrices are stored in column major order. E.g., a  $3 \times 3$  matrix A is stored

$$a_{11} \to a_{21} \to a_{31} \to a_{12} \to a_{22} \to a_{32} \to a_{13} \to a_{23} \to a_{33}$$

There are programming languages where matrices are stored row-wise, e.g., C and Pascal. In the following, we assume the Fortran storage convention.

#### 2.3.1 Interleaved Memory

The primary memory of many high performance computers is interleaved: it consists of separate banks, which can operate independently of each other. Reading or writing a word from a bank takes a certain number of clock cycles.

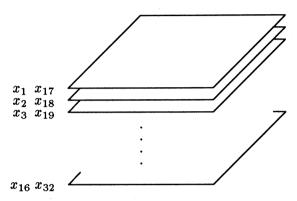

The consecutive elements of a vector are stored in consecutive banks, see Figure 2.9

Figure 2.9: The storage of a vector in interleaved memory with 16 banks.

As an example, on the Cray X-MP/416 the primary memory is interleaved with 64 banks.

Since the different banks can operate independently, it is possible to load consecutive elements of a vector from memory to vector registers (or the other way around), so that one word is delivered each clock cycle. On the other hand, if one loads non-consecutive elements of the vector, it may happen that when a word is requested from a memory bank, the bank has not finished processing the previous request. This is called a **memory bank conflict**. There is special hardware to resolve bank conflicts: the second request must wait until the first is finished.

Memory bank conflicts may occur whenever non-unit stride references to a vector are made. Note that since matrices are stored in column major order, referencing a matrix row-wise is equivalent to referencing a vector with non-unit stride.

With interleaved memory also vload (vector load) and vstore (vector store) operations can be chained. The execution of the assembler code

Figure 2.10: Timing diagram for four chained vector operations.

can then be illustrated by the timing diagram in Figure 2.10.

If memory bank conflicts occur during the execution of a vector load or store operation, then the floating point operations are delayed (but not interrupted).

In order to perform the above code as a chained vector operation there must be two read channels and one write channel between the primary memory and the vector registers, provided that the memory can deliver operands at high enough speed.

A similar type of conflict occurs if, in a computer with multiple processors, two different processors access the same bank, and again that conflict is resolved by special hardware. Note that interleaved memory with many banks is particularly useful in computers, where several processors share the same memory, since this reduces the risk of this type of memory conflict.

We finish this section with a diagram (Figure 2.11) showing the basic structure of a vector register architecture.

### 2.3.2 Memory Hierarchy

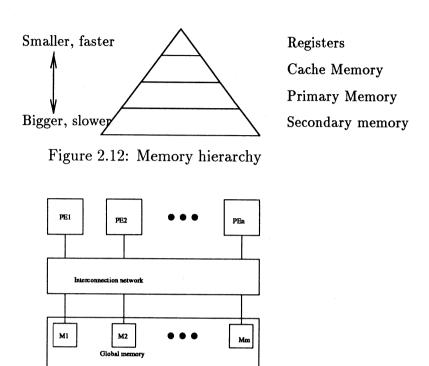

Another important concept in high performance computers is **memory hierarchy**. Due to the cost of manufacturing very fast memory hardware, computer designers often must compromise between memory speed and size. Many modern high performance computers, therefore, have a memory hierarchy, see Figure 2.12. (We remark that some computers have vector registers and no cache memory, while others have cache and no vector registers. There are computers that have both.)

Obviously, it is desirable to perform as many floating point operations

Figure 2.11: Vector register architecture. Pipelined units are shaded.

as possible for every floating point variable that is transferred from primary memory to the registers or cache memory.

# 2.4 Shared Memory Parallel Computers

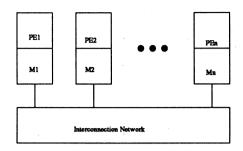

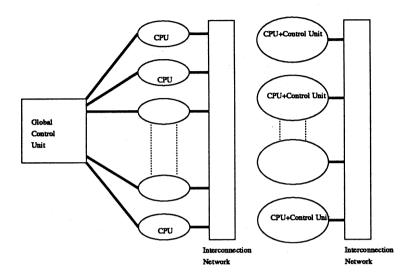

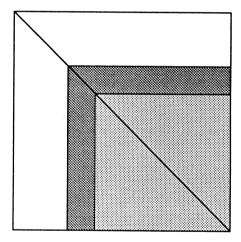

Multiprocessor architectures with shared memory are tightly coupled systems in which there is complete connectivity between processors and memory modules. A simplified block diagram is shown in Figure 2.13.

The primary memory may be centralized (only one memory module) or partitioned into several modules. The common memory is accessed by all processors. The interconnection network is a potential bottleneck for these systems. Memory contention (memory access conflict) is important because of the need of many processors to simultaneously access the same memory locations. The interaction between processors and processes are controlled by a common operating system.

The major limitation of the shared-memory system is the possibility of

Figure 2.13: Shared memory systems

primary memory access conflicts and this tends to put an upper bound on the number of processors that can be effectively incorporated in the system. Examples of shared-memory systems include the Alliant, the Encore Sequent, the Cray-1, Cray-2, Cray Y-MP, Fujitsu VP2600, NEC SX-3.

# 2.5 Distributed Memory Parallel Computers

Distributed memory parallel computers are efficient for problems that can be partitioned into larger tasks that do not interact verý frequently. A typical distributed memory system consists of several computer modules and an interconnection network, see Figure 2.14.

Each computer module has a processor, a memory, and an I/O interface. Data communication is carried out through message passing. Each message usually consists of a number of fixed-size packets. Inter processor communication follows a predetermined communication protocol.

Figure 2.14: Distributed memory system

#### 2.5.1 Interconnection Networks

We present several interconnection topologies that are commonly used in message passing system.

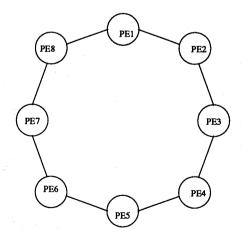

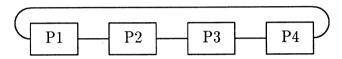

**Linear and Ring Arrays** In a linear array, p processors are connected along a line and in a ring array, they are connected around a ring as shown in Figures 2.15 and 2.16.

Figure 2.15: Linear array of processors

Figure 2.16: A processor ring

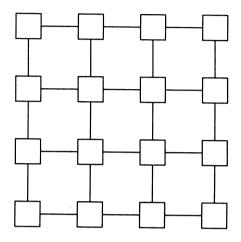

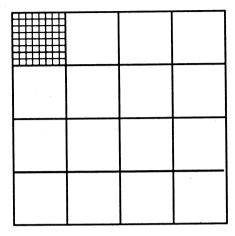

Two-dimensional arrays A two-dimensional array consists of an array of

$p \times p$  processors connected as shown in Figure 2.17. Often, the wrap around connection is assumed in order to yield more homogeneous complexity results.

Figure 2.17: A two-dimensional array

Hypercubes Hypercubes are based on the binary n-cube topology and they are called by several different names such as Cosmic cube, n-cube, binary n-cube, etc. The first hypercube system was built at Caltech in the early 1980s as an experimental parallel computer for scientific computations.

A hypercube multiprocessor consists of  $2^n$  processors, consecutively numbered with binary integers using a string of n bits. Each processor is connected to every other processor whose binary number differs from its own by exactly one bit. Hypercube interconnection networks for n = 1, 2, 3, 4 are shown in Figure 2.18 A hypercube of order 0 has one node, and the hypercube of order n+1 is constructed by taking two hypercubes of order n and connecting their respective nodes.

The hypercube interconnection network has several important properties such as the fact that the number of connection wires increases only logarithmically as the number of processors increases. Furthermore, several other interconnection networks such as linear and ring arrays, two-dimensional arrays, and trees, can be embedded efficiently in the hypercube, which means that the embedding can be done in a way so that that neighbors in the embedded graph become neighbors in the host graph (the hypercube).

The path length for a message between any two nodes is exactly the number of bits in which their tag bits differ. The maximum is n and numerous possible paths connecting any two nodes exist.

Figure 2.18: Hypercube interconnection

Fat Trees Consider a binary tree and locate computation processors at the leaves (squares in Figure 2.19). Place communication control processors at the other nodes (filled circles).

Real trees become thicker further from the leaves. Fat trees resemble real trees in the sense that the bandwidth increases further from the leaves. One common scheme is to double the communication capacity (bandwidth) for every level as we ascend from the leaves to the root.

Assume that the wires are full duplex at the leaf level. This means that any two neighboring leaves, e.g. P0 and P1 in Figure 2.19, can send and receive messages from each other at the same time. Since the bandwidth is doubled on the next level, there is enough capacity to let P0 and P2 communicate with each other at the same time as P1 and P3 communicate. Similarly, it is easy to see that the bandwidth is large enough for the situation when each processor is communicating with one other processor.

The Connection Machine CM-5 has a network based on the fat tree.

## 2.6 SIMD and MIMD Parallel Computers

Processors in various parallel processing architectures operate either under the centralized control or work independently. In SIMD (Single Instruction and Multiple Data streams) architectures, there is a single control processor which dispatches instructions to each processor. The same instruction is executed by all processors. Processors in MIMD (Multiple Instruction and Multiple Data

Figure 2.19: Binary fat tree. The processors are located at the leaves. The circles represent communication control processors, and the arcs are the communication channels.

streams) architectures do not have this kind of external control and they can execute different programs asynchronously. Any synchronization results from a possible need for exchanging data with other processors.

In MIMD computer, each processor has its own control unit and it is possible to use general purpose microprocessors in MIMD computers as processing units. MIMD computers offer a much higher degree of flexibility than SIMD computers since in SIMD computers, all the processors should execute same instruction in the same clock cycle. This means that each condition should be executed serially in a conditional statement. Many unstructured applications are better suited to MIMD computer. SIMD computer offer free synchronization after each instruction execution and it is better for parallel programs that require frequent synchronization.

### 2.7 Performance Measurements

## 2.7.1 Speedup and Efficiency

In ideal situation, one expects to gain a factor of p in time when using p processors to solve a given problem. If  $T_1$  and  $T_p$  are the time for executing the algorithm on one processor and p processors, respectively, then the speedup is

Figure 2.20: Typical SIMD and MIMD architectures

$$S_p \equiv T_1/T_p$$

.

Often the parallel algorithms are not the best ones on one processor and this can lead to the following alternative which compares the best possible algorithm on one processor to the parallel algorithm on p processors

$$S_p^a \equiv T_s/T_p,$$

where  $T_s$  denotes the time required for the best serial algorithm that solves the problem.

The efficiency is the speed-up divided by the number of processors,

$$E_p = S_p/p$$

or  $E_p^a = S_p^a/p$ .

#### 2.7.2 Amdahl's Law

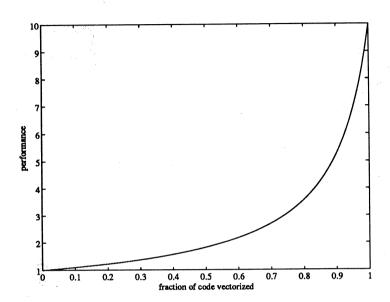

It is interesting to study the performance of a code on a vector or parallel computer, where only a certain fraction can be vectorized or parallelized. Given a program, does it pay to run it on a supercomputer (in the sense that it utilizes the hardware efficiently)?

Assume that we have a vector processor and that operations in scalar mode and in vector mode take  $t_s$  and  $t_v$  (in some unit), respectively. Then the peak

performance of this computer is

$$r_{\infty}=rac{1}{t_{v}}.$$

Further assume that the fraction  $f_v$  of the total number of operations in the code can be run in vector mode. Then the total time to execute the code is

$$T = N[(1 - f_v)t_s + f_v t_v],$$

where N is the number of operations performed in the code. The average time per operation is

$$t_f = [(1 - f_v)t_s + f_v t_v],$$

and the performance of the computer on this code is

$$r_f = \frac{1}{(1 - f_v)t_s + f_v t_v}.$$

In Figure 2.21 we plot  $r_f$  as a function of  $f_v$ . We have assumed that vector operations are 10 times faster than scalar operations. It is seen that only for  $f_v$  (the fraction of the code that is vectorizable) close to 1 does the performance get in the neighborhood of  $r_{\infty}$ .

Assume that we have a code, which is vectorizable to 80%. With the values of the parameters in Figure 2.21, we then get a performance of only 36% of peak performance. Thus, Amdahl's law give a rather pessimistic picture of the usefulness of supercomputers. However, it is a little misleading in many situations.

When one is evaluating a new supercomputer, it is very likely one has in mind running bigger problems than are possible on the presently available computer. Also, often the fraction of the code that is vectorizable depends on the problem size.

Assume that the number of operations for a certain program depends on the problem size n in the following way:

$$A(n) = an^3 + bn^2,$$

where the first term represents the vectorizable part, and the second the non-vectorizable. One can think of Gaussian elimination with partial pivoting, where the transformations of the matrix elements require  $O(n^3)$  operations

Figure 2.21: Amdahl's law. We have used  $t_s = 10t_v$ , and scaled so that peak performance  $r_{\infty}$  is equal to 10.

and can be vectorized well. The pivot search, on the other hand, takes  $O(n^2)$  operations and vectorizes badly.

For a certain value of n 80% of the code is vectorizable (i.e.,  $an^3/(an^3 + bn^2) = 0.8$ ). This gives the following relation:  $an^3 = 4bn^2$ .

If we consider a problem that is 10 times larger, then we get

$$A(10n) = 10^3 an^3 + 10^2 bn^2,$$

and the fraction vectorizable code is

$$\frac{10^3 a n^3}{10^3 a n^3 + 10^2 b n^2} = \frac{1000}{1000 + 25} \approx 0.976.$$

With the same parameters as in Figure 2.21 we now get 82% of peak performance.

On a parallel computer, let us assume that the fraction of serial part in an algorithm is  $f_1$ . If the total execution time on one processor is  $t_1$ , the execution time for the intrinsically sequential part is  $f_1t_1$  and the rest is  $(1-f_1)t_1$ . On

p processors, the sequential part cannot be parallelized, so its execution time will be the same and the parallel part can be parallelized by a factor of p, which gives

$$t_p = f_1 t_1 + (1 - f_1) t_1 / p.$$

Thus, the speed up is bounded by

$$s_p \le 1/(f_1 + (1 - f_1)/p))$$

which means that for any algorithm and any number of processors,

$$s_p \le 1/f_1$$

and this indicates that the efficiency will decrease asymptotically to  $1/(pf_1)$ .

#### 2.7.3 Scaled Speed-up

According to Amdahl's law for a parallel computer, the only way to increase efficiency is to reduce  $f_1$ . Often, a way to reduce  $f_1$  is to increase the problem size. Note that the parallel overhead will have more effect when the problem size is smaller. This observation lead to the definition of scaled speed-up.

In Amdahl's law, by assuming that the fraction of the sequential part is a constant, it assumes a given problem size which takes a certain fixed time on a sequential machine. If we assume that what is fixed is the time on a p-processor machine,  $t_p^s$  is the time to execute a given program on a p-processor machine, and  $f_1^s$  is the fraction of the sequential part, then the time for the same program run on a single processor would be

$$t_1^s = f_1^s t_p^s + p(1 - f_1^s) t_p^s$$

and the speed up is

$$s_p^s = (f_1^s t_p^s + p(1 - f_1^s) t_p^s) / t_p^s = f_1^s + (1 - f_1^s) p.$$

In the scaled speed up, we assume that the time to solve the given problem on a *p*-processor computer is fixed, which means that the problem size increases as the number of processors increase.

We can further modify the above speed up and calculate the speed-up by allowing the problem that is as large as can be fit in memory. Define

$$s_p^G = w_p T_1 / T_p$$

where  $T_i$  is the time for executing  $Q_i$ ,  $Q_i$  is the maximum size problem that can be solved on an *i*-processor computer, and  $w_p$  is the adjustment factor, which accounts for the difference in the number of arithmetic operations due to the difference in problem sizes. The number of operations for solving  $Q_p$  is  $w_p$  times the number of operations required to solve  $Q_1$ . The adjustment by  $w_p$  guarantees that we are comparing two executions that will perform the same number of operations.

# 2.8 Important Issues in Parallel Computers

Identification of Parallelism The parallelism can be expressed either by users or compilers. Automatic parallelization of sequential programs for multiprocessors has been only partially successful.

Partitioning After parallelism is identified, we need to partition the computational task into processes and identify the objects that they share.

Memory Allocation The creation of new processes requires allocation of memory space. Memory allocation is influenced by the memory organization and by the interconnection network.

Memory Access In shared-memory multiprocessors, this is particularly important since processors compete for same memory locations. A problem in multiprocessors is that of maintaining memory consistency in systems where different processors attempt to read and write from and to the same memory locations.

Scheduling The main goal is to assign processes to processors so that communication time and overhead are minimized.

Synchronization It is necessary to maintain the correct execution order by imposing the satisfaction of data dependencies.

# Chapter 3

# Vectorization and Fortran

# 3.1 Introduction

FORTRAN, created in the late 1950s first, is one of the most widely used programming languages for solving problems in science and engineering. A new standard has recently been finalized and the version of FORTRAN 90 has many new features. We will use FORTRAN as a model language in describing the details of vectorization.

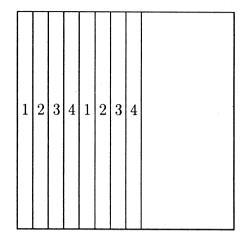

# 3.2 Storage of Matrices

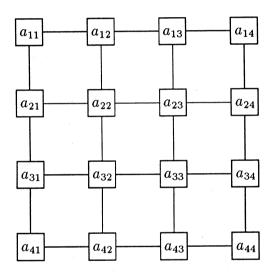

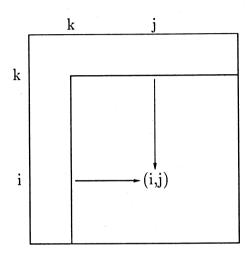

In Fortran matrices are stored in column major order. E.g., a matrix A declared as

real A(1:4,1:3)

is stored

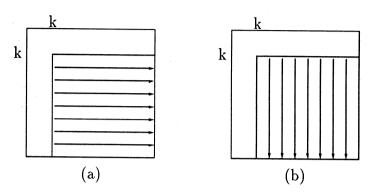

If we reference the matrix column-wise,

then we have stride 1. If we reference row-wise

then we have stride 4.

Exercise: What is the stride if we reference diagonal-wise:

### 3.3 Fortran 90

A new Fortran standard has been adopted and it is called Fortran 90 (the previous one was Fortran 77). It has several constructs that are aimed at making vectorization and parallelization easier. Here we describe some new features, which are important for vector and parallel computers.

### 3.3.1 Vectors and Matrices

One of the most important new concepts in Fortran 90 is that arrays (vectors and matrices) are data objects in themselves, and they can be referenced as such, not just as a collection of subscripted scalars.

Let a, b and c be declared

real

$$a(1:m,1:n)$$

,  $b(1:m,1:n)$ ,  $c(1:m,1:n)$

Arithmetic operations for matrices can be written

a=b\*c c=a-b

Matrix multiplication is element-wise.

All the intrinsic functions can be used for matrices. Let a be declared as above. The code

gives as result a matrix b, the elements of which are

$$b(i,j)=sin(a(i,j))$$

## 3.3.2 Array Sections

Array sections can be referenced using a notation analogous to that in the do-loop:

i:j:k

where i is the start index, j the final index and k is the stride. This can be used to write

$$x(1:20:2)=y(1:10)$$

which in Fortran 77 was written

There is one important difference here, however: using the array section the order in which the operations to the elements are performed is not prescribed.

There are variants:

i:j

which means that stride 1 is assumed. If the first variable is omitted:

; j

then the lower limit in the declaration of the array is assumed. The variant

.

means that both the lower and upper limit in the declaration are assumed. Thus, if a is declared real a(100), then the following references are equivalent,

and they all refer to the whole vector.

Let the matrix x be declared x(1:100,1:50). Then the first of the following references

```

x(1:50,1:10)

x(:,25:30:2)

```

is a reference to the upper left submatrix of dimensions  $50 \times 10$ , and the second to the column vectors  $\mathbf{x}(1:100,25)$ ,  $\mathbf{x}(1:100,27)$  and  $\mathbf{x}(1:100,29)$ .

If a scalar is used in a assignment statement together with arrays, it is considered as an array of appropriate dimensions. The assignment

$$a(:)=3.14$$

gives each element of a the value 3.14. A further example is as follows:

```

real a(100), b(-1:98), x(100,50,25), y(100,100,10,70), p,q

...

a=1.0

b(:10)=p+q

x(:,n,1)=a+b

x(m:n,1:10,1:20)=y(1,m:n,1:10,41:60)

```

Note that all arrays used in an assignment must have conforming dimensions. The following rule is important in understanding the difference between array sections used in assignments and do, and in understanding how array sections are executed using vector instructions.

### Rule: In the assignment

```

array section=expression

```

the whole expression in the right hand side is computed before the assignment takes place (imagine that the operations are performed in vector registers).

```

Thus, the assignment

a(2:n)=a(1:n-1)+a(3:n+1)

is not equivalent to

do i=2,n

a(i)=a(i-1)+a(i+1)

enddo

but equivalent to

do i=2,n

temp(i)=a(i-1)+a(i+1)

enddo

do i=2,n

a(i)=temp(i)

enddo

(in the sense that they give the same results).

```

# 3.3.3 Vector Mask Operations

The construct

```

where (a(1:n) > b(1:n)) a(1:n)=x

gives the same result as

do i=1,n

if (a(i) .gt. b(i)) a(i)=x

enddo

Similarly

where (a(1:n) > b(1:n))

a(1:n)=x

elsewhere

a(1:n)=b(1:n)

endwhere

gives the same result as

do i=1,n

if (a(i) .gt. b(i)) then

a(i)=x

else

a(i)=b(i)

endif

enddo

```

These code sections can be implemented on vector machines using vector mask operations.

# 3.4 Vectorization of Loops

In general, Fortran code where the assignments can be expressed with array sections can be executed using vector instructions. However, not all algorithms are or can be expressed conveniently using array sections. The task of a **vectorizing compiler** is to analyze do loops, and generate vector instructions where this is possible.

#### 3.4.1 Vector Reference

Earlier we saw that a memory reference for a vector, i.e. a vector load or store, has a start address, a length (the number of words that need to be transferred), and a constant stride. In principle we have

VL elements from the vector x are loaded to the vector register Vreg, starting with element x(1). The stride is stride.

**Definitions:** An integer variable, which has a constant increment in a loop, is called a CII (Constant Increment Integer).

A vector reference is a reference inside a loop where all indices are of the form

$[\pm invariant expression *] CII [\pm invariant expression]$

It is easy to see that with this definition all vector references have a start address, a vector length, and a constant stride.

In the example

all the references to arrays are vector references:

| array   | s length            | stride       |       |

|---------|---------------------|--------------|-------|

| w       | w(1)                | n            | 1     |

| X       | $\mathbf{x}(1,n)$   | $\mathbf{n}$ | 1     |

| У       | y(m, 30 - 5 * n, l) | $\mathbf{n}$ | 750   |

| ${f z}$ | z((6-n)*l-9)        | n            | 3 * l |

Loops where all array references are vector references can be executed using vector instructions.

## 3.4.2 Indirect Addressing

Indirect addressing means that a vector is referenced via a vector of indices. In Fortran 77 we write

```

do i=1,64

a(ia(i))=b(ib(i))+c(ic(i))

enddo

```

where ia, ib, and ic are integer arrays holding the indices of the elements in the arrays that we use in the assignment statement. The corresponding Fortran 90 code is

$$a(ia)=b(ib)+c(ic)$$

Loading data this way (b and c) is called **gather**, and storing (a) is called **scatter**, cf. Section 2.2.4. Since the stride is not constant, these operations are not vector references. In spite of this, they can be vectorized using special machine instructions (e.g. on the Cray Y-MP).

Indirect addressing occurs in solving sparse systems of linear equations (a system is called sparse if most of the matrix elements are zero), and in the FFT algorithm for computing the discrete Fourier transform.

## 3.4.3 Scalar Temporary Variables

A scalar variable may inhibit vectorization in a loop where all the array references are vector references. Consider, e.g., the code

```

do i=1,n

sca=a(i)*b(i)+sqrt(x(i)**2+y(i)**2)

r(i)=sca*y(i)

z(i)=(d(i)+e(i))/sca

enddo

```

If at each iteration of the loop, the value of sca is to be stored in a scalar register, then vectorization is not possible. However, by creating a temporary vector, a pseudo vector, the compiler can generate vector instructions:

```

V1=a(1:n)*b(1:n)+sqrt(x(1:n)**2+y(1:n)**2)

r(1:n)=V1*y(1:n)

z(1:n)=(d(1:n)+e(1:n))/V1

sca=[last element of V1]

```

#### 3.4.4 Recursion

Since the semantics of Fortran prescribe sequential execution, data dependence between two Fortran statements of the type

implies that the statements must be executed in this order. When a loop is executed, then it assumed that the iterations are performed in the order specified in the do statement. Therefore, a loop can be vectorized if no data are used that have been modified in a previous iteration.

It is obvious that the iterations in the code

are completely independent and can be vectorized (and also parallelized). Similarly, the following loop can be vectorized

since the elements on the right hand side in the assignment are unmodified during previous iterations of the loop. However, in the loop

elements that have previously been modified are on the right hand side. This is called **recursion** and cannot be vectorized.

An example of a very important application, where recursion occurs, is the solution of a bidiagonal linear system of equations

$$\begin{pmatrix} a_1 & & & & \\ b_2 & a_2 & & & \\ & b_3 & a_3 & & \\ & & \ddots & \ddots & \\ & & & b_n & a_n \end{pmatrix} \begin{pmatrix} x_1 \\ x_2 \\ x_3 \\ \vdots \\ x_n \end{pmatrix} = \begin{pmatrix} d_1 \\ d_2 \\ d_3 \\ \vdots \\ d_n \end{pmatrix}$$

This can be solved by the code

Such a recursion can only be executed in scalar mode.

In order for the compiler to generate vector instructions, it must be clear at compile time that the code can be vectorized. Consider

```

do i=1,n

a(i)=c(i)+b(ib(i))

b(i)=x(i)*y(i)

d(i)=e(i)/a(i+k)

enddo

```

Here it is in general impossible for the compiler to determine if k will be negative or positive (unless k is explicitly assigned a constant value in the program, and this is the only assignment where it occurs). Similarly, the compiler will have difficulties with the indirect addressing in the first statement. It is possible that for some previous i, b(ib(i)) has been modified (e.g., if ib(2)=1).

In such cases the compiler cannot decide if recursion will take place or not. But if the programmer knows that no recursion will occur, then the programmer should give the compiler directives to vectorize (and he/she becomes responsible for errors, not the compiler).

#### **Exercises:**

1. Can the code

be vectorized?

2. Let the vector of indices be ia=(1,2,1). Can the code

be vectorized?

3. Consider the matrix equation

$$BX = D$$

,

where B is bidiagonal and all the matrices are  $n \times n$  (for simplicity). This can be regarded as a sequence of bidiagonal systems

$$Bx_j = d_j, \quad j = 1, 2, \ldots, n,$$

where  $x_j$  and  $d_j$  are the column vectors X and D, respectively. The matrix equation can be solved by changing the algorithm in the text above so that each x(i) is replaced by x(i,j) and the corresponding for d, and by adding a j loop outside the i loop. Do this.

Then rewrite the code by exchanging the order of the loops. Does it vectorize now? If so, why?

### 3.4.5 Reduction of a Vector to a Scalar

A common difficulty in vectorization is reduction operations where a vector is reduced to a scalar, e.g. summation

```

sum=0.0

do i=1,n

sum=sum+x(i)

enddo

or matrix multiplication

do j=1,n

do i=1,n

a(i,j)=0.0

do k=1,n

a(i,j)=a(i,j)+b(i,k)*c(k,j)

enddo

enddo

enddo

enddo

```

If n is very large, then the compiler can optimize this operation so that most of the operations are vector instructions.

**Example:** Consider the summation  $\sum_{i=1}^{n} x(i)$ , where n = 1000 \* 64. the computation can be vectorized

```

0 --> V0

do i=1,1000,2

vload x((i-1)*64+1:i*64) --> V1

vadd V0 + V1 --> V2

vload x(i*64+1:(i+1)*64) --> V3

vadd V2 + V3 --> V0

enddo

Add the elements of V0 using a special operation

```

Exercise: Why are two vadd operations performed in the loop?

When n is less than 64, then reduction operations cannot be vectorized in the same way as ordinary vector operations (that would presuppose that arithmetic operations could be performed with operands in the same vector register). But since this type of operations is so common, many vector computers have special machine instructions for performing them, so that they execute faster than scalar operations, but not quite as fast as ordinary vector instructions.

Note, however, that if the scalar variable is used in more than one statement of the loop, then this can inhibit the use of such special instructions.

```

sum=0.0

do i=1,n

sum=sum+x(i)*y(i)

z(i)=sum*t(i)

enddo

```

Here the components of the vector z are functions of the partial sums, and therefore all these must be made available.

## 3.4.6 Rounding Errors

The result of a computation executed by vector operations may not be exactly the same as when the computation is performed in scalar mode, since the individual arithmetic operations may be performed in different order.

Assume that we have a computer with 15 decimal digits of accuracy in floating point representation. The code

```

a(2:10000)=1.0E-16

a(1)=1.0

sum=0.0

do i=1,10000

sum=sum+a(i)

enddo

```

will give the result sum=1, if executed in scalar mode. If performed using vector instructions (using e.g. the code from the beginning of the preceding section) it is likely that the result is different. By summing the elements in this order, enough small elements will be added so that some partial sums are greater than  $10^{-15}$ , and thus will give a noticeable contribution when added to 1.

### 3.4.7 Vectorization Inhibitors

a loop cannot be vectorized if it has

- 1. recursion

- 2. a subroutine call

- 3. I/O operations

- 4. assigned goto statements (†)

- 5. certain nested if blocks

- 6. goto statements that lead out of the loop

- 7. goto into the loop (†)

- ((†) denotes statements/constructs that no responsible programmer would use anyway.)

# Chapter 4

# Numerical Algorithms on Vector Computers

# 4.1 Matrix Multiplications

### 4.1.1 Matrix-vector Product

To illustrate how linear algebra computations should be organized to execute efficiently on vector computers, we use the example of matrix-vector product y = Ax, where A has dimension  $m \times n$ . The components of y are given by

$$y_i = \sum_{j=1}^n a_{ij} x_j, \quad i = 1, 2, \dots, m.$$

The algorithm

```

{* ij variant *}

do i=1,m

y(i)=0

do j=1,n

y(i)=y(i)+a(i,j)*x(j)

enddo

enddo

```

performs this computation. Symbolically we can write:

$$\begin{pmatrix} \times \\ \times \\ \times \\ \times \end{pmatrix} = \begin{pmatrix} \longleftarrow & - & - & \rightarrow \\ \longleftarrow & - & - & \rightarrow \\ \longleftarrow & - & - & \rightarrow \\ \longleftarrow & - & - & \rightarrow \end{pmatrix} \begin{pmatrix} \uparrow \\ \downarrow \\ \downarrow \end{pmatrix}.$$

This figure should be interpreted as follows: each element of the right hand side vector is equal to the inner product of x and one row of the matrix A.

This algorithm has a couple of disadvantages:

- 1. The elements of A are referenced row-wise, which means that there is a risk of memory bank conflicts.

- 2. Even though inner products can be vectorized (using special instructions and hardware), they are usually slower than "real" vector operations.

We can exchange the order of the loops by writing the matrix as a collection of column vectors

$$A=(a_{.1}\ a_{.2}\ \cdots\ a_{.n}),\quad a_{.j}=\left(egin{array}{c} a_{1j}\ a_{2j}\ dots\ a_{mj} \end{array}

ight),$$

we can write the multiplication in the form

$$y = (a_{.1} \ a_{.2} \ \cdots \ a_{.n}) \begin{pmatrix} x_1 \\ x_2 \\ \vdots \\ x_n \end{pmatrix} = \sum_{j=1}^n a_{.j} x_j.$$

This is done by the code

The inner loop is a Saxpy operation: a vector plus a scalar times a vector (S denotes single precision). The code can be written using vector assignments:

Symbolically:

$$\begin{pmatrix} \uparrow \\ \downarrow \\ \downarrow \end{pmatrix} = \begin{pmatrix} \uparrow & \uparrow & \uparrow & \uparrow \\ \downarrow & \downarrow & \downarrow & \downarrow \\ \downarrow & \downarrow & \downarrow & \downarrow \end{pmatrix} \begin{pmatrix} \times \\ \times \\ \times \end{pmatrix}.$$

Here we have vector operations, which can be chained and executed very efficiently.

The semantics of Fortran prescribe that at each iteration of the loop, the vector  $\mathbf{y}$  is converted to the floating point format in which it has been declared. Therefore, if, as is often the case, the vector register is wider than the standard word length, the conversion must take place, and this is usually done by storing  $\mathbf{y}$  in the primary memory. Since we are only interested in the final value of  $\mathbf{y}$ , there are n-1 unnecessary vstore operations.

Instead we would prefer to accumulate y in a vector register. This variant is sometimes called **Gaxpy** (Generalized Saxpy). (In the code below we assume that a scalar can be stored in the multiplication unit and used in a vector operation.)

```

{* Gaxpy-variant *}

0 --> V0

do j=1,n,2

vload a(1:m,j) --> V1

load x(j) to multiplication unit

V1*x(j) --> V2

```

```

V2+V0 --> V3

vload a(1:m,j+1) --> V4

load x(j+1) to multiplication unit

V4*x(j+1) --> V5

V5+V3 --> V0

enddo

vstore V0 --> y(1:m)

```

#### Exercises

- 1. Which of the above variants is more efficient when  $m \ll n$ ?

- 2. How should the matrix-vector multiplication be organized if m is much larger than the length of the vector registers?

Compilers will usually recognize when a chaining operation can be done. Unfortunately, compilers do not always recognize when intermediate results could stay in vector registers nor when the overlapping of loads and arithmetic operation can be done. To simulate Gaxpy, **loop unrolling** can be done. For simplicity, assume that n is a multiple of 4. The ji-variant code can then be written

Here the compiler can keep the vector y in vector registers while four chained vector multiplications and additions are executed, and it is only necessary to store it in primary memory when j changes.

## 4.1.2 Matrix Multiplication

Consider the problem of computing the matrix product

$$A = BC$$

where, for simplicity, we assume that all matrices are square with order n. A common matrix multiplication algorithm can be written as

```

{* Sdot variant *}

do i=1,n

do j=1,n

a(i,j)=0

do k=1,n

a(i,j)=a(i,j)+b(i,k)*c(k,j)

enddo

enddo

enddo

```

In the same manner as we did with matrix-vector multiplication, we can now change the order of the loops in 3! = 6 different ways. The above variant is based on scalar products (Sdot).

Disregarding the zero initialization of A, we can write the generic matrix multiplication algorithm

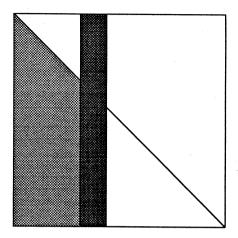

If we restrict ourselves to column oriented variants without scalar products, two variants are left (we denote them by the order of the indices): kji and jki (note that by making i the last index, we have column oriented vector operations in the innermost loop).

We can illustrate the computation of the two innermost loops symbolically:

$$\mathtt{kji:} \qquad \begin{pmatrix} \uparrow & \uparrow & \uparrow & \uparrow \\ | & | & | & | \\ | & | & | & | \\ \downarrow & \downarrow & \downarrow & \downarrow \end{pmatrix} = \begin{pmatrix} & & & \uparrow & \\ & & & \downarrow & \\ & & & \downarrow & \end{pmatrix} \begin{pmatrix} & & & \\ \times & \times & \times & \times \end{pmatrix}$$

The figure should be interpreted: "each column of A is updated by adding a multiple of a column from B".

We see that the operation is Saxpy, and that each column of A must be fetched from primary memory, updated and then stored back.

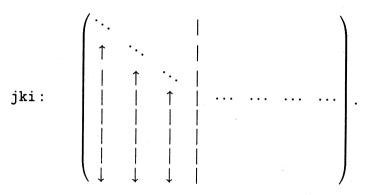

The two innermost loops of the jki variant can be illustrated:

$$\mathtt{jki:} \qquad \left( \begin{array}{cccc} & & \uparrow & \\ & & \downarrow & \\ & & \downarrow & \end{array} \right) = \left( \begin{array}{cccc} \uparrow & \uparrow & \uparrow & \uparrow \\ \downarrow & \downarrow & \downarrow & \downarrow \\ \downarrow & \downarrow & \downarrow & \downarrow \end{array} \right) \left( \begin{array}{cccc} & \times & \\ \times & \times & \\ \times & \times & \end{array} \right)$$

This should be interpreted: "a column from A is computed by summing multiples of the columns of B".

This variant can be implemented using Saxpy operations, but we see that since the computation of each column of A is finished before it is stored back, we have a Gaxpy oriented algorithm. Furthermore, since the columns of B need only be loaded from primary memory, and not stored back, we have only half as much memory traffic as in the kji variant.

The memory traffic in the three variants described above, Sdot (ijk), kji and jki, is summarized in Table 4.1.2 (only the highest order term is given).

| Sdot  | kji    | jki   |

|-------|--------|-------|

| $n^3$ | $2n^3$ | $n^3$ |

Table 4.1: Memory traffic in matrix multiplication.

# 4.2 BLAS: Basic Linear Algebra Subprograms

BLAS consists of a number of subroutines for basic linear algebra computations. The first level of BLAS were developed for LINPACK, which is a library of subroutines for the solution of linear systems of equations.

One of the main reason for developing BLAS was to make it easier for the designer of linear algebra programs to write well-structured and efficient code using a set of modules for the most common computations.

Another reason was that the BLAS routines can be implemented (often in assembler language) by the different computer manufacturers so that they utilize the hardware as efficient as possible. Thus all machine-dependent details can be hidden inside the BLAS routines, and the programs based on BLAS will be completely portable, i.e., they can be executed on all different computers without changes.

There are BLAS routines in single precision (with prefix S, e.g. Saxpy), double precision (Daxpy), complex single precision (Caxpy), and complex double precision (Zaxpy).

#### Level 1 BLAS

The first level of BLAS routines are vector-scalar operations and vector-vector operations (e.g. Saxpy and Sscal; the latter scales a vector by a scalar).

As an example we take Snrm2, whose declaration begins

```

real function snrm2(n,sx,incx)

```

where n is the number of elements of the vector sx, the norm of which is to be computed, and incx is the increment (stride) in the vector. The norm of a row of a matrix can be computed as follows:

```

real a(100,50)

.....

len=snrm2(50,a(3,1),100) {* the norm of row 3 *}

```

We list the level 1 BLAS in the following where x and y are vectors:

#### Level 2 BLAS

When computers with vector instructions became available, it was soon evident that Level 1 BLAS did not utilize the hardware efficiently (cf. the discussion of Saxpy and Gaxpy above). This lead to the definition of a set of routines on a higher level, and thus the Level 2 BLAS routines perform matrix-vector operations.

Some examples of Level 2 BLAS operations are

• matrix-vector multiplication,  $y = \beta y + \alpha Ax$ , where  $\alpha$  and  $\beta$  are scalars, x and y are vectors and A is a matrix. The subroutine is called Sgemv in the case when the matrix is general (i.e., non-symmetric). The discussion above about Saxpy and Gaxpy operations shows that much can be gained by implementing matrix-vector multiplication in assembler language.

- outer product,  $A = A + \alpha x y^T$ , where x and y are column vectors. The subroutine is called Sger ("r" denotes "rank 1 update").

- solution of a system  $x = T^{-1}x$ , where the matrix T is triangular. The subroutine is called Strsv ("tr" for triangular and "sv" for solve).

#### Level 3 BLAS

In analogy to Level 1 BLAS for vector-vector operations and Level 2 BLAS for matrix-vector operations, there is Level 3 BLAS for matrix-matrix operations. Typical examples are

- Matrix product  $A = \beta A + \alpha BC$ . The subroutine is called Sgemm ("ge" for general matrix, "mm" for matrix multiplication).

- Solution of triangular systems with several right hand sides  $B = T^{-1}B$ . The subroutine is Strsm ("sm" for the solution of system with multiple right hand sides).

## BLAS and memory references

One of the most important conclusions of this section is that in order to write efficient programs on high performance computers, it is necessary to take into account the traffic of operands from primary memory to functional units and back. The following rule should be observed.

Rule: For each memory reference, perform as many floating point operations as possible.

We will now consider the different levels of BLAS from the point of this rule. In each call of Saxpy, two vectors are loaded and one is stored. Thus 3n memory references are made (in the sequel we assume that the vectors have n elements and the matrices have order n). The routine performs n multiplications and n additions, altogether 2n flops. The Level 2 BLAS routine Sgemv for matrix-vector multiplication load a whole matrix ( $n^2$  memory references;

we disregard the vectors here). The number of flops is  $2n^2$  approximately. Finally, the Level 3 BLAS routine for matrix multiplication, Sgemm, loads three matrices and stores one, altogether  $4n^2$  memory references. Here we have  $2n^3$  flops.

We summarize in Table 4.2, where we also give Megaflop rates on three high performance computers. The data are taken from [6].

| BLAS  | routine | ref.   | flops  | flops/ref | Cray-2   | IBM 3090VF | Alliant FX/8 |

|-------|---------|--------|--------|-----------|----------|------------|--------------|

| level |         |        | _      |           | peak 488 | peak 108   | peak 88      |

| 1     | Saxpy   | 3n     | 2n     | 2/3       | 121      | 26         | 14           |

| 2     | Sgemv   | $n^2$  | $2n^2$ | 2         | 350      | 60         | 26           |

| 3     | Sgemm   | $4n^2$ | $2n^3$ | n/2       | 437      | 80         | 43           |

Table 4.2: Memory traffic and floating point operations. Megaflop rates for three computers. Unfortunately the source did not show the size of the problems.

It is very simple to parallelize Level 3 BLAS routines. Matrix multiplication can be considered as a number of independent matrix-vector multiplications, which can be executed in parallel by different processors. Similarly, the solution of triangular systems with multiple right hand sides are independent and can be distributed to different processors.

# 4.3 Linear Systems of Equations

# 4.3.1 Gaussian Elimination and LU Decomposition

Suppose we would like to solve a linear system of equations

$$Ax = b$$

where the matrix A has order n, and is assumed to be non-singular (see [9]). For simplicity we will not consider pivoting in the algorithm for Gaussian elimination. After k-1 steps in the algorithm we have reduced the matrix to

the form

$$egin{pmatrix} a_{11} & a_{12} & & \dots & & a_{1n} & b_1 \ & a_{22} & & \dots & & & \vdots & \vdots \ & & \ddots & & & & \vdots & \vdots \ & & & a_{kk} & a_{k,k+1} & \dots & a_{kn} & b_k \ & & \vdots & & \vdots & & \vdots & \vdots \ & & & a_{ik} & a_{i,k+1} & \dots & a_{in} & b_i \ & & & \vdots & & \vdots & \vdots & \vdots \ & & & & a_{nk} & a_{n,k+1} & \dots & a_{nn} & b_n \ \end{pmatrix}.$$

In the next step of the elimination the elements below the main diagonal in column k will be annihilated. The result is

$$\begin{pmatrix} a_{11} & a_{12} & & \dots & & a_{1n} & b_1 \\ & a_{22} & & \dots & & a_{2n} & b_{2n} \\ & & \ddots & & & \vdots & \vdots \\ & & a_{kk} & a_{k,k+1} & \dots & a_{kn} & b_k \\ & \vdots & \vdots & & \vdots & \vdots \\ & 0 & a'_{i,k+1} & \dots & a'_{in} & b'_i \\ & \vdots & \vdots & & \vdots & \vdots \\ & 0 & a'_{n,k+1} & \dots & a'_{nn} & b'_n \end{pmatrix},$$

where the transformed elements are given by

$$a'_{ij} = a_{ij} - a_{ik}a_{kj}/a_{kk},$$

$j = k+1,...,n,$   $i = k+1,...,n,$

$b'_{i} = b_{i} - a_{ik}b_{k}/a_{kk},$   $i = k+1,...,n,$

Thus Gaussian elimination can be performed by the following program (for simplicity we omit the transformations of the right hand side vector b):

```

do k=1,n-1

do j=k+1,n

do i=k+1,n

a(i,j)=a(i,j)-a(i,k)*a(k,j)/a(k,k)

enddo

enddo

enddo

```

As in the matrix multiplication, we can change the order of the loop and describe Gaussian elimination by the following generic algorithm:

```

do -----

do -----

do -----

a(i,j)=a(i,j)-a(i,k)*a(k,j)/a(k,k)

enddo

enddo

enddo

enddo

```

We can permute the loop variables i, j and k in 3! = 6 different ways. We will discuss how the efficiency of the different alternatives depends on the architecture.

We discuss three variants. First consider the kij variant (in the literature it is often called the text book variant). Here the matrix is referenced as follows in the two innermost loops:

kij:

$$\begin{pmatrix} \ddots & & & & & & \\ & \ddots & & & & & \\ & & \ddots & & & \\ & & \leftarrow & - & - & - & \rightarrow \\ & & \leftarrow & - & - & - & \rightarrow \\ & & \leftarrow & - & - & - & \rightarrow \\ & & \leftarrow & - & - & - & \rightarrow \end{pmatrix}.$$

As in the case of matrix multiplication, the kji variant is a Saxpy oriented algorithm:

Another name for this variant is right-looking, since in each step the matrix elements to the right of the column that is annihilated in the present transformation are referenced (updated).

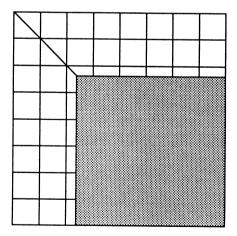

The Gaxpy variant, alternatively the jki variant, references the matrix in the following way: